|

灵活控制输出电压的启动顺序,Startup sequence

关键字:灵活控制输出电压的启动顺序

一些IC厂商建议以特定的电压启动顺序为其器件提供电源电压,用户线接口电路(SLIC)就是一个很好的例子。SLIC的电源电压通常包括若干负电压和/或正电压,这取决于最终使用及安装位置,比如,电话响铃通常需要较高的电压,而摘机状态的电话机供电仅需较低的电压。

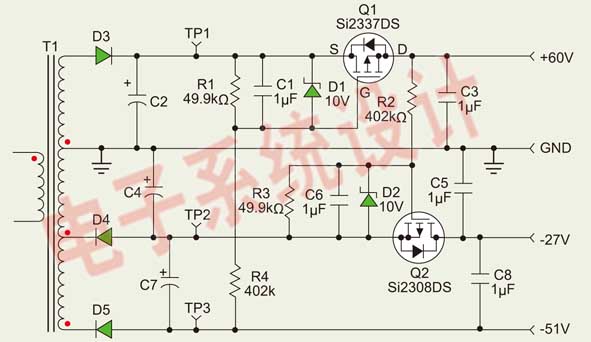

比如,假设一款设计的输出电压为-51V、+60V及-27V,且各输出电压的负载电流均为几百毫安。负载要求一个特定的电压启动顺序,即首先是-51V,然后是+60V,最后为-27V的电压启动顺序。这三个输出电压均来自回扫式转换器的变压器次级绕组(图1),输出电压是一起启动的,因此一个电压处于关闭状态而不影响其它两个电压是不可能的。

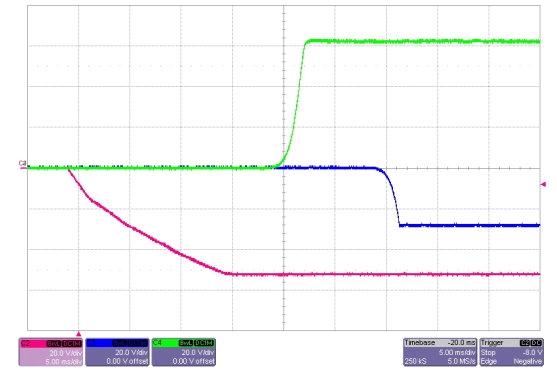

当处于开启状态时,回扫式输出电压同时升高的情况如图2所示。图2的输出电压是在图1中测试点1(TP1)至TP3之间测量到的电压。

|

| 图1:在典型的回扫式转换器输出电路中增加一对FET和相关器件,可提供有延迟的两个输出电压。 |

为获得所需的启动顺序,必须延迟启动+60V和-27V的输出电压。在TP1点添加一个与+60V整流输出电压串联的P通道FET(Q1)来延迟输出电压,直至-51V达到稳压状态。电阻器R1与R4形成了+60V到-51V之间的分压器,并按比例分压,这样,当+60V与-51V都出现时,Q1的栅源极电压可充分提高Q1的电压。R1、R4及C1的并联组合在Q1启动之前增加了可编程延迟,采用如图1所示的元件值将产生5~10ms的延迟。因为该延迟由所选FET的启动阈值控制,所以我们在确定延迟时间实际范围的时候,必须特别注意这点。齐纳二极管D1可防止Q1栅源极出现过压,但如果有必要,可去掉齐纳二极管。

|

| 图2:输出电压的同时启动的顺序(+60V、-27V及-56V)。 |

如同Q1延迟+60V输出一样,Q2可以延迟-27V输出。Q2栅极由+60V开关输出电压控制。因为使之启动的栅极“触发”电压是正向的而不是负向的,所以FET Q2必须是N通道FET。图3显示了预期的输出电压交错启动顺序。

|

| 图3:输出电压按预期的顺序开始启动。 |

采用这种方法时应注意一些问题。当FET Q1与Q2处于关闭状态时,TP1与TP2处的输出电压没有负载,因此峰值检测带来的电压毛刺可能会导致整流电压过冲。这些毛刺值通常是由于变压器的漏极电感而引起的。可以通过在二极管两端增加缓冲器,或者增加与输出电容器并联的预负载电阻器,来尽量减少漏极电感的影响。随着负载电流的升高,FET Q1的漏源极电压会降低,Q2的电压会升高。如果在选择额定导通电阻很低的FET的时候不加以注意,随着负载的增加,电压稳压的性能会降低。采用较高的输出电压(>10V)及低负载电流(<0.5A)可实现电路的最佳工作状态(推荐采用此配置),这样FET压降就可以忽略不计。在断电期间,输出电压关闭的先后顺序取决于输出端的负载。

这个电路为产生电压顺序延迟提供了灵活性,可以被用在输出电压有很大差别的任何电源输出电路中。

作者:John Betten

德州仪器公司

|